采用碳纳米管制造的16位RISC-V处理器

我们不断缩小硅基处理器功能的能力似乎已成为过去,材料科学家正在考虑如何超越硅片。最重要的候选者是碳纳米管,它自然地以半导体形式存在,具有出色的电性能,并且非常小。不幸的是,已经证明在需要它们的地方种植纳米管非常困难,并且难以操纵它们将它们放置在正确的位置。已经有一些进展,在解决这些挑战的工作,但结果通常被所示 相当有限的示威。

现在,研究人员已经使用碳纳米管制作了一个符合RISC-V标准的通用处理器,可以处理32位指令并进行16位存储器寻址。性能无关紧要,但处理器成功执行了传统编程演示的变体“Hello world!”。这是一项令人印象深刻的工作,但并非所有研究人员的解决方案都可能导致高性能处理器。

我们可以解决这个问题

碳纳米管存在许多问题。首先,虽然纳米管自然地以半导体形式存在,但它们是作为该过程和金属纳米管的使用的混合物而生产的。虽然可以净化半导体版本,但纯度水平在99.9%纯度附近趋于平稳。这对许多情况都很好,但是当处理器有数百万个纳米管时,显然不会削减它。纳米管不会自然形成p型或n型半导体(分别部分地传输正电荷或负电荷)。在硅中,这些特性是通过添加少量额外元素来驱动的,这一过程称为掺杂。但纳米管非常小,难以掺杂。

其他问题来自于需要将纳米管置于极其精确的位置以使任何电子器件工作。我们还没有弄清楚如何让它们在任何特定的位置生长,因此科学家不得不分别制作它们,然后让它们沉淀在表面上。不幸的是,这个过程通常会产生一个随机取向的纳米管薄膜,由大量聚集的聚集体打断。并且将会有一些随机放置的金属纳米管潜伏在胶片内。

新的处理器是由麻省理工学院的研究人员和ADI公司的科学家合作完成的,他们找到了解决所有这些问题的方法。

第一个解决方法是接受纳米管的混乱。研究人员制造的硅表面具有足够大的金属特征,可以保证几个纳米管通常能够弥合金属之间的间隙,而不是试图在每个需要的位置放置一根管子。为了去除聚集体,他们在纳米管顶部沉积了一层材料,然后通过超声将其破碎。这种材料带有聚集体,但它使纳米管的下层不受干扰。

接下来,为了将纳米管限制在需要的地方,研究人员只需将大部分纳米管蚀刻掉,只留下需要的地方。然后,他们在纳米管顶部添加了可变的氧化物层。氧化物的精确性质与用于连接的不同金属相结合,可以根据需要将纳米管转化为p型或n型半导体。虽然这个过程更类似于掺杂一个恰好含有纳米管的区域,但它可以有效地控制各个结的行为。

那些金属纳米管仍然潜伏在所有这些中吗?研究人员刚刚将它们留在原地,并在芯片设计方面做了一些工作。

逻辑逻辑布局

虽然芯片的功能单元执行添加两个数字的操作,但这些单元由较小逻辑门的集合构成,这些逻辑门执行简单的功能:NOT翻转位的值,如果两个输入值均为逻辑AND,则取值为1 1,依此类推。通常有多种方法来构造这些逻辑门以形成相同的功能单元。因此,可以使用5个AND和7个NOR的正确排列来添加两个数字,也可以使用6个NOT和4个NAND来完成。(注意:这些数字完全弥补。)

新芯片背后的研究人员的主要见解是某些逻辑功能对金属纳米管的敏感度低于其他功能。因此,他们修改了一个开源RISC设计工具来考虑这些信息。结果是芯片设计没有对金属碳纳米管最敏感的栅极。

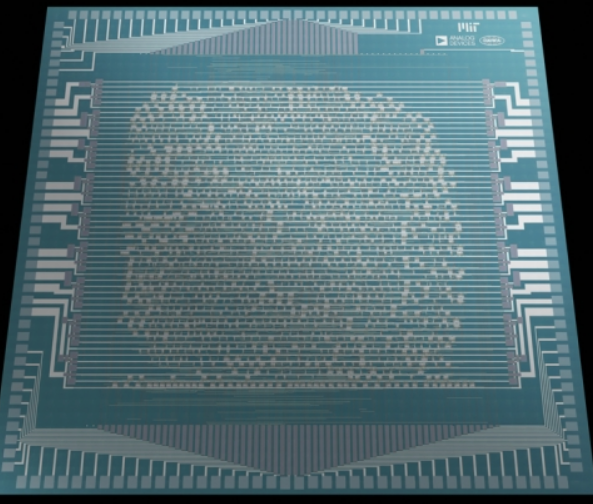

由此产生的芯片称为RV16X-NANO,该芯片旨在处理RISC-V架构的32位长指令。存储器寻址限制为16位,功能单元包括指令获取,解码,寄存器,执行单元和写回存储器。总体而言,RV16X-NANO使用了超过14,000个单独的晶体管,并且碳纳米管的操作使得它们产生100%的产率。换句话说,这14,000个门中的每一个都有效。

它也被认为是3D芯片,因为纳米管层下面的金属触点用于在不同晶体管之间路由信号,而在纳米管上方分层的单独金属触点层用于在芯片内供电。

最关键的是,它有效。从上图中可以看出,它成功地执行了传统“Hello World”程序的变体,该程序通常用作对不同编程语言语法的简单介绍。

路线图还是绕行?

在他们的论文中,研究人员专注于改善现有设计的所有方法。例如,沟道长度是由纳米管桥接的金属触点之间的距离。该长度有助于设置时钟速度,对于RV16X-NANO,时钟速度仅为10kHz。金属触点也必须非常宽,以确保有足够的纳米管桥接它们。理论上我们知道两者都有可能改进,并且通过这种方法提高时钟速度是一个明确的选择。

但由于这种设计需要容忍金属纳米管(而不是去除它们),因此每个晶体管总是需要多个纳米管。该设计还需要足够宽,使得具有一些处于不良取向的纳米管仍将留下足够的空间以供其他人形成功能性接触。这意味着功能必然会比我们想要的更大,并且需要更长时间才能在状态之间切换。

在通过架构解决金属纳米管的存在所涉及的总晶体管数量方面也可能存在成本,尽管这可能根据给定功能单元的目的而变化。

这些问题有不同的解决前景。这个过程没有任何阻止门长度缩小的过程,这会导致时钟速度的增加; 这是研究人员可以立即尝试的东西。如果我们能想出一种制造纯半导体纳米管源的方法,其他一些问题就会自行解决。这显然是人们正在努力的事情,但在问题得到解决之前,这种设计仍将受到限制。

但这里的最终目标是制造单纳米管晶体管,这需要能够控制它们在芯片上的位置。这项工作没有任何内容可以让我们更接近这一点。

总的来说,这是一项令人印象深刻的工程设计和重要的验证,我们可以将碳纳米管与我们现有的芯片制造工艺以及处理器运行所需的其他电子元件集成在一起。但在解决阻碍碳纳米管充分发挥其潜力的问题方面,它并没有走得太远。