英特尔首次推出针对AI工作负载的Stratix 10 NX FPGA

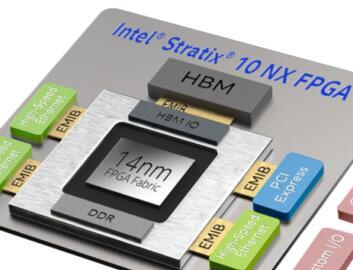

英特尔今天推出了其首款经过AI优化的FPGA – Stratix 10 NX,它具有扩展的AI Tensor模块(30个乘法器和30个累加器),集成的HBM存储器和高带宽网络。新芯片继续利用英特尔的小芯片架构,并且该芯片的FPGA部分使用英特尔的14纳米技术制造。

英特尔报告称,新的FPGA将提供比Stratix 10 MX多15倍的INT8计算能力.Stratix 10 MX于2017年末推出,其DSP模块只有两个乘法器和两个累加器。新芯片还具有“高达57.8 Gig PAM4收发器和硬核英特尔以太网模块的高效率”。英特尔称,Stratix 10 NX将于今年晚些时候上市。

“出现的最具破坏力的趋势是AI模型的大小和复杂性呈指数级增长,”英特尔数据平台事业部可编程解决方案事业部总经理,企业副总裁David Moore在媒体预告中说。“我们看到的是,AI模型的复杂度每三个半月翻一番,或者每年翻一番。因此,在BERT 和 GPT之类的最大和下一代变压器模型中,它的参数将达到数百亿甚至更多 。”

“我们当前的(MX)计算模块实际上是为通用计算而设计的。因此,它具有广泛的灵活性,可以满足各种信号处理应用程序,操作和精度[要求]的苛刻要求。AI张量块的设计专注于加速AI应用程序,优化有效的张量流水线以及降低AI空间中常用的精度,整数和浮点格式。这些创新使我们能够将15倍的计算量打包到与标准DSP计算块相同的空间中。”

在更专业的应用领域中,FPGA有望作为低成本,高性能器件发挥越来越大的作用。FPGA的优势之一是能够实现低延迟处理并降低与通用CPU中未使用的硅片相关的成本。长期以来,由于难以编程/开发而享有盛誉,较新的工具使FPGA开发更加容易。到目前为止,仍然没有实现希望FPGA能够导致更普遍的可重配置系统的希望。

“我们通常会看到FPGA在实时,低批量应用中与众不同。因此,FPGA的灵活性和可配置的存储器层次结构使开发人员能够真正定制其设计,以创建优化的低延迟解决方案。”

针对Nvidia,英特尔表示,用于BERT批处理的Stratix 10 NX器件比Nvidia V100 GPU快2.3倍,在LSTM批处理中快9.5倍,在ResNet50批处理中快3.8倍。(请参见下面的幻灯片)

英特尔现已全面向异构架构迈进。Moore表示:“很明显,至强,人工智能和FPGA开发人员社区正在聚在一起解决异构计算难题。我们的重点不仅包括用于硬件和软件集成的工具,还包括从标准库和框架集成这些工具以无缝支持应用程序开发的工具。”

英特尔将赌注押在oneAPI(它正在倡导的基于标准的统一编程模型)上,以促进异构Xeon平台与各种加速器(如FPGA)的集成。

当被问及NX与MX有何不同以及与Microsoft的Project Brainwave * 完成的英特尔FPGA开发工作有何关系时 ,Moore将NX描述为MX和Microsoft工作的演变,而不是与众不同。

当然,英特尔近年来已收购了多家加速器公司和技术,包括最近的Habana Labs。

在简报中被问及关于Habana的计划时,英特尔公司副总裁兼至强和内存事业部总经理Lisa Spelman说:“ Habana专注于AI培训或推理工作量。我们的数学和TCO计算表明,当您查看工作负载流时,如果AI成为工作负载的[足够高]百分比,则可以通过加速或专用加速来补充基础处理器,从而提高经济效益。[它]与工作量的大小,要通过训练功能或推理尝试处理的数据量以及工作量的流有关。

“有些东西,就像我再次提到推荐系统一样,因为工作量的流以及将响应内置到响应中的方式,CPU实际上是这些工作量降落的最自然且最有可能的位置。如果您认为[潜在的]在非常特定的培训环境中进行图像处理,那么像Habana这样的专用于手头任务的加速器可能会成为最佳的总拥有成本模型,即使该模型仅用于较窄的部分中。问题。”

*微软Project Brainwave:

“ Brainwave项目是一个深度学习平台,用于在云和边缘上进行实时AI推理。基于高性能现场可编程门阵列(FPGA)的软神经处理单元(NPU)加速了深度神经网络(DNN)推理,并应用于计算机视觉和自然语言处理中。Brainwave项目正在通过使用互连的,可配置的,由可编程芯片组成的计算层来扩展CPU,从而改变计算方式。

“例如,这种FPGA配置在Bing的RNN上在延迟和吞吐量方面实现了超过一个数量级的改进,而无需进行批处理。通过提供实时AI和超低延迟而无需批量处理,可减少软件开销和复杂性。”